当我们谈论数据中心,那些支撑起我们日常数字生活的庞大设施时,其最核心、最繁忙的部件就是服务器,而服务器的“大脑”,也就是中央处理器(CPU),其架构设计直接决定了整个数据中心的效能、成本和未来发展的潜力,深入理解服务器CPU架构,就像是掌握了开启高效能数据中心大门的钥匙。

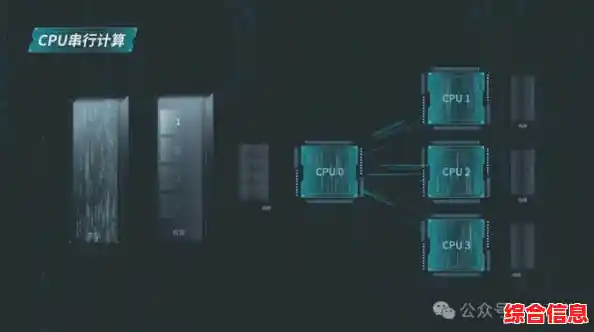

在过去很长一段时间里,服务器CPU的世界相对简单,遵循着一个主要的思路:追求更高的单核性能,这意味着芯片设计师们努力让单个计算核心运行得越来越快,处理指令的效率越来越高,这种架构对于当时主流的商业应用,比如数据库、网页服务等,非常有效,因为很多任务无法被拆分,只能由一个强大的核心按顺序处理,英特尔至强处理器就是这种架构的典型代表,它们凭借强大的单线程性能占据了市场主导地位。

随着互联网的爆炸式增长,特别是云计算、大数据、人工智能等新兴技术的普及,数据中心的计算需求发生了根本性的变化,任务的性质从“重单核”转向了“多线程”和“高并发”,想象一下,一个云服务提供商需要同时响应成千上万用户的请求,或者一个AI模型需要处理海量的图片或文本数据,这些任务往往可以被分解成大量的小任务,同时进行处理。

这就催生了CPU架构的演进:从追求极致的单核性能,转向增加核心数量,这种多核架构就像是将许多个“大脑”集成在一颗芯片上,让它们协同工作,共同处理一项庞大的工程,AMD的EPYC处理器就是这一趋势的积极推动者,率先推出了拥有大量核心的CPU,这种架构的优势在于,它能以更高的整体效率来处理那些可以并行化的任务,在相同的功耗下提供更强的总计算能力,对于云数据中心来说,这意味着可以在单台服务器上托管更多的用户或服务,显著降低了每项计算任务的成本。

但仅仅增加核心数量还不够,随着核心越来越多,另一个瓶颈出现了:核心之间如何高效通信?以及CPU如何快速访问内存和存储?这就涉及到CPU架构中另一个关键层面:互联架构和内存子系统。

传统的架构中,所有核心都通过一条共享的总线来访问内存和相互通信,当核心数量少时,这没问题,但当核心数量激增,这条“高速公路”就会变得异常拥堵,核心们不得不花费大量时间等待数据传输,计算效率反而下降,为了解决这个问题,现代服务器CPU开始采用更先进的互联技术,比如模块化设计,它将CPU芯片分成几个较小的、功能完整的“小芯片”,每个小芯片内部有自己的一组核心和内存通道,这些小芯片之间通过一条极高速的内部互联链路沟通,这种设计好比将一个大城市划分为几个功能完善的城区,城区内部交通顺畅,城区之间有高速地铁连接,极大地缓解了交通压力,提升了整体效率。

内存访问也变得更加重要,为了喂饱几十个“饥饿”的计算核心,需要提供足够宽的内存带宽,现代服务器CPU普遍支持更多通道的内存,并且将内存控制器直接集成在CPU内部,缩短了数据路径,降低了延迟,对新型内存技术(如DDR5)的支持也变得至关重要。

除了通用计算核心,另一个显著的趋势是“异构计算”的融入,传统的CPU是“通才”,什么任务都能处理,但可能不是最高效的,针对特定任务的“专家”被集成到CPU的架构中,或者以紧密耦合的方式与CPU协同工作,一些CPU开始集成AI加速引擎,专门用于处理人工智能负载中的矩阵计算,其效率远高于通用核心,还有的架构为数据库加速、加密解密、数据压缩等常见数据中心任务设计了专用硬件单元,这种“通才”+“专家”的组合,使得CPU架构能够更加智能地分配任务,将合适的计算交给最擅长的单元去完成,从而实现极致的能效比。

功耗和散热已经成为CPU架构设计的硬约束,数据中心的电费是运营成本的大头,而计算密度越高,散热挑战越大,现代的服务器CPU架构将能效放在与性能同等重要的位置,这包括精细化的功耗管理,比如让CPU能够动态调整每个核心的频率和电压,在负载低时进入节能状态;也包括先进的制程工艺,在更小的芯片面积上集成更多晶体管,从而降低单位计算的功耗。

服务器CPU架构的演进是一部为了适应数据中心需求而不断自我革新的历史,它从单一的性能冲刺,发展到多核并行;从解决内部通信拥堵,到拥抱异构计算;始终围绕着如何在海量数据洪流中,更高效、更经济、更智能地完成计算任务,选择什么样的CPU架构,决定了数据中心的计算能力、能源消耗和未来扩展的弹性,深入理解这些核心要素,不仅是技术专家的课题,也是任何希望构建未来数字基础设施的决策者必须关注的焦点。